- Home

- Laptops

- Laptops News

- Intel, AMD Reveal Details of CPU Design Advancements at ISSCC 2015

Intel, AMD Reveal Details of CPU Design Advancements at ISSCC 2015

Intel and AMD are amongst the companies presenting papers and participating in discussions at the ongoing 2015 International Solid-State Circuits Conference in San Francisco. Both companies will be disclosing plans for future chip designs and manufacturing processes, as well as learnings from products rolled out in the recent past.

Intel has shared previews of its planned presentations, which largely deal with the viability of Moore's Law as transistor widths shrink to 10nm and below. Intel co-founder Gordon Moore predicted in 1965 that the transistor count of high-end processors would double every two years, and that has largely held true till now despite the mounting challenges of fabricating smaller transistors.

While Intel's migration to 14nm transistors was delayed, it has now rolled out successfully with the Broadwell (Core) and Cherry Trail (Atom) product lines. The company has now stated that it expects the 10nm transition to occur smoothly in 2016, followed by a shrink to 7nm in 2018. Now with Moore's Law in its 50th year, Intel believes there is no reason for it to break down. Beyond 7nm, techniques for improving process tech such as etching with lasers in the extreme ultraviolet wavelength range might become necessary.

According to AnandTech, Intel is also considering 3D stacked dies or using multiple fabrication methods to reduce overall size and power leakage. These methods will be considerably more expensive than the current method of laying out dies on interposer layers, but could still be suitable for certain applications such as low-power portable devices.

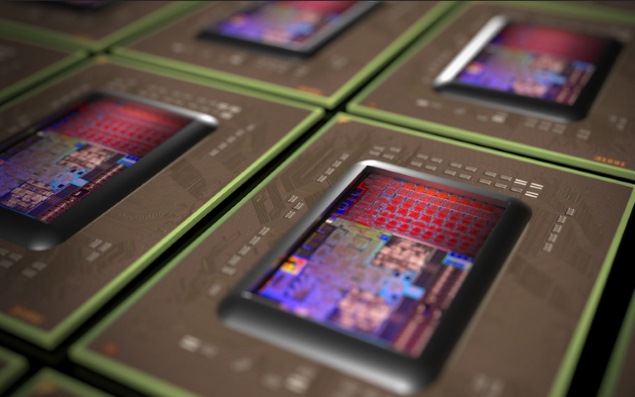

AMD detailed the features and enhancements of its next-generation "Carizzo" A-series processor. Carizzo will launch by the middle of 2015 and will be a true SoC (System-on-a-Chip) with integrated Radeon graphics. AMD expects a 40 percent reduction in power consumption as well as "substantial" gains in processing and graphics capabilities compared to current A-series "Kaveri" products.

Specifically, Carizzo will have 29 percent more transistors than Kaveri without increasing die size, and while continuing to use the 28nm manufacturing process. The efficient usage of space created more area for a new Radeon graphics core as well as IO functions generally handled by the motherboard southbridge.

AMD is also optimising power by analysing voltage fluctuations on the nanosecond scale and compensating on the fly, rather than supplying too much current to compensate. Sensors will go beyond the usual measurements of thermal output and current draw in order to help the processor dynamically scale to workloads.

Carizzo will introduce support for Heterogenous Unified Memory Access, which allows the CPU and GPU components to address a joint pool of memory space rather than reserving their own pools. Instructions and data thus do not have to be transferred from one pool to another when required by different execution units, thus reducing latency and improving performance.

For the latest tech news and reviews, follow Gadgets 360 on X, Facebook, WhatsApp, Threads and Google News. For the latest videos on gadgets and tech, subscribe to our YouTube channel. If you want to know everything about top influencers, follow our in-house Who'sThat360 on Instagram and YouTube.

Related Stories

- Samsung Galaxy Unpacked 2025

- ChatGPT

- Redmi Note 14 Pro+

- iPhone 16

- Apple Vision Pro

- Oneplus 12

- OnePlus Nord CE 3 Lite 5G

- iPhone 13

- Xiaomi 14 Pro

- Oppo Find N3

- Tecno Spark Go (2023)

- Realme V30

- Best Phones Under 25000

- Samsung Galaxy S24 Series

- Cryptocurrency

- iQoo 12

- Samsung Galaxy S24 Ultra

- Giottus

- Samsung Galaxy Z Flip 5

- Apple 'Scary Fast'

- Housefull 5

- GoPro Hero 12 Black Review

- Invincible Season 2

- JioGlass

- HD Ready TV

- Laptop Under 50000

- Smartwatch Under 10000

- Latest Mobile Phones

- Compare Phones

- Moto G15 Power

- Moto G15

- Realme 14x 5G

- Poco M7 Pro 5G

- Poco C75 5G

- Vivo Y300 (China)

- HMD Arc

- Lava Blaze Duo 5G

- Asus Zenbook S 14

- MacBook Pro 16-inch (M4 Max, 2024)

- Honor Pad V9

- Tecno Megapad 11

- Redmi Watch 5

- Huawei Watch Ultimate Design

- Sony 65 Inches Ultra HD (4K) LED Smart TV (KD-65X74L)

- TCL 55 Inches Ultra HD (4K) LED Smart TV (55C61B)

- Sony PlayStation 5 Pro

- Sony PlayStation 5 Slim Digital Edition

- Blue Star 1.5 Ton 3 Star Inverter Split AC (IC318DNUHC)

- Blue Star 1.5 Ton 3 Star Inverter Split AC (IA318VKU)